JPL Publication 86-31

## **Electricity from Photovoltaic Solar Cells**

# Flat-Plate Solar Array Project Final Report

Volume V: Process Development

11 Years of Progress

October 1986

Project Managed by the Jet Propulsion Laboratory for the U.S. Department of Energy

Jet Propulsion Laboratory California Institute of Technology

4800 Oak Grove Drive Pasadena, California 91109 (818) 354-4321

March 2, 1987

To: Recipients of JPL Publication 86-31

Subject: Erratum

The title page showing the authors of Volume V, Process Development, of the Flat-Plate Solar Array Project Final Report, JPL Publication 86-31, is in error. Mr. G. Gallagher, as shown, should be written as B. Gallagher.

les R. Cumine

L. R. Lunine, Manager Foothill Documentation Section 641

## Photovoltaic Module Progress

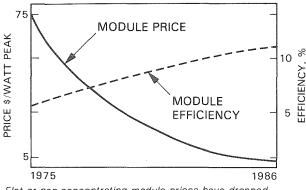

Flat or non-concentrating module prices have dropped as module efficiencies have increased. Prices are in 1985 dollars for large quantities of commercial products.

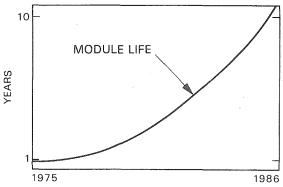

Typical module lifetimes were less than 1 year but are now estimated to be greater than 10 years. (Ten-year warranties are now available.)

## Technology advancement in crystalline silicon solar cells and modules (non-concentrating).

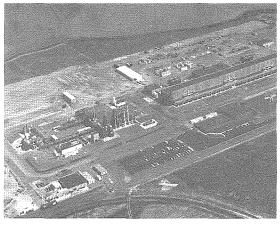

Union Carbide Corporation (UCC) funded the now operational silicon refinement production plant with 1200 MT/year capacity. DOE/FSA-sponsored efforts were prominent in the UCC process research and development.

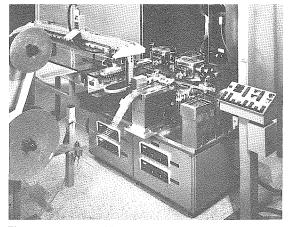

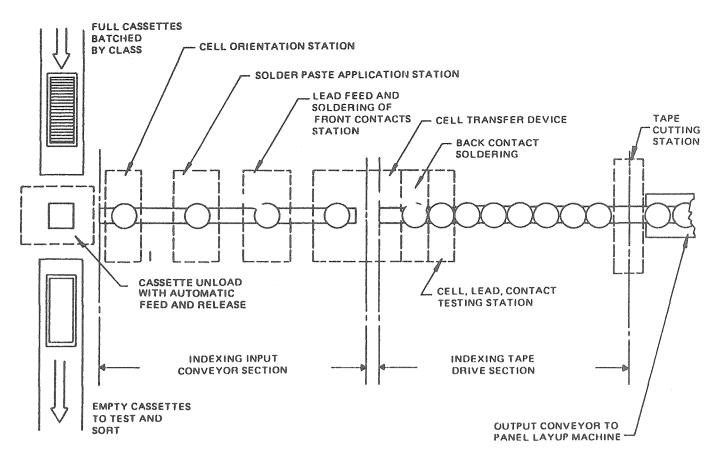

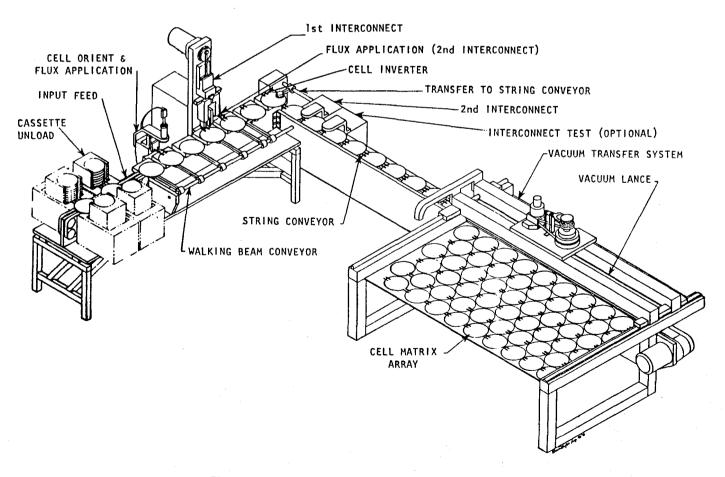

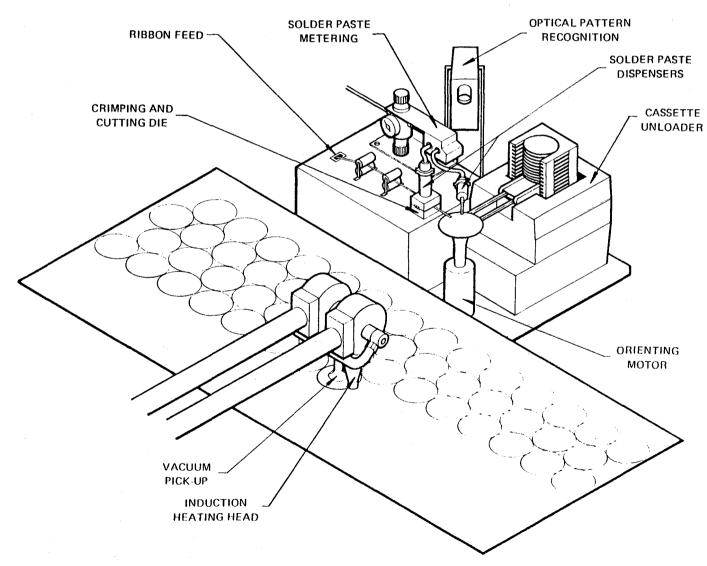

The automated machine interconnects solar cells and places them for module assembly. The secondgeneration machine made by Kulicke and Soffa was cost shared by Westinghouse Corporation and DOE/FSA.

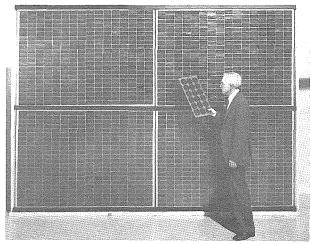

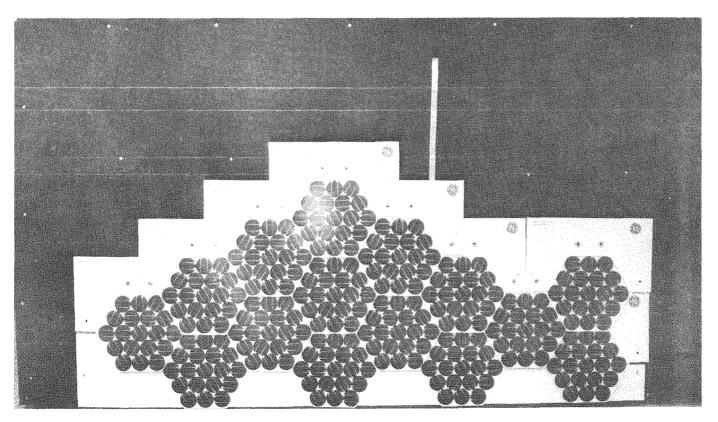

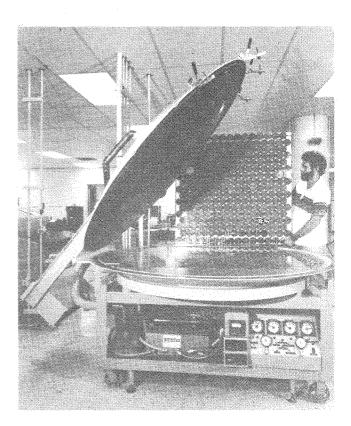

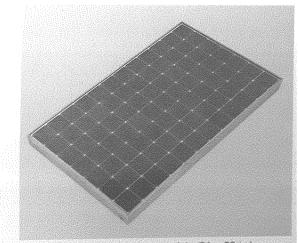

A Block I module (fabricated in 1975), held in front of four Block V modules, represents the progress of an 11-year effort. The modules, designed and manufactured by industry to FSA specifications and evaluated by FSA, rapidly evolved during the series of module purchases by DOE/FSA.

More technology advancements of the cooperative industry/university/ DOE/FSA efforts are shown on the inside back cover. Use of modules in photovoltaic power systems are shown on the outside back cover. 5101-289 Flat-Plate Solar Array Project DOE/JPL-1012-125 Distribution Category UC-63b

Electricity from Photovoltaic Solar Cells

# Flat-Plate Solar Array Project Final Report

## **Volume V: Process Development**

- G. Gallagher P. Alexander

- D. Burger

11 Years of Progress

October 1986

Prepared for

U.S. Department of Energy Through an Agreement with National Aeronautics and Space Administration

by

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

JPL Publication 86-31

Project Managed by the Jet Propulsion Laboratory for the U.S. Department of Energy's National Photovoltaics Program

## Final Report Organization

This FSA Final Report (JPL Publication 86-31, 5101-289, DOE/JPL 1012-125, October 1986) is composed of eight volumes, consisting of an Executive Summary and seven technology reports:

Volume I: Executive Summary.

Volume II: Silicon Material.

- Volume III: Silicon Sheet: Wafers and Ribbons

- Volume IV: High-Efficiency Solar Cells.

- Volume V: Process Development.

- Volume VI: Engineering Sciences and Reliability.

- Volume VII: Module Encapsulation.

- Volume VIII: Project Analysis and Integration.

Two supplemental reports included in the final report package are:

FSA Project: 10 Years of Progress, JPL Document 400-279, 5101-279, October 1985.

Summary of FSA Project Documentation: Abstracts of Published Documents, 1975 to 1986, JPL Publication 82-79 (Revision 1), 5101-221, DOE/JPL-1012-76, September 1986.

Upon request, this FSA Final Report (JPL Publication 86-31) and the two supplemental reports (JPL Document 400-279 and JPL Publication 82-79) are individually available in print from:

National Technical Information Service U.S. Department of Commerce 5285 Port Royal Road Springfield, VA 22161

## Abstract

The Flat-Plate Solar Array (FSA) Project, funded by the U.S. Government and managed by the Jet Propulsion Laboratory, was formed in 1975 to develop the module/array technology needed to attain widespread terrestrial use of photovoltaics by 1985. To accomplish this, the FSA Project established and managed an Industry, University, and Federal Government Team to perform the needed research and development.

The goal of the Process Development Area, as part of the FSA Project, was to develop and demonstrate solar cell fabrication and module assembly process technologies required to meet the cost, lifetime, production capacity, and performance goals of the FSA Project. Early in the Assessment Phase, it became apparent that available processes were incapable of meeting the cost goals of the Project. Also, neither the 20-year (later increased to 30-year) reliability goal nor the effects of processing on reliability had ever been assessed.

This document is a summary of the FSA-sponsored research and development efforts expended by Government, Industry, and Universities in developing processes capable of meeting the Project's goals during volume production conditions. The cost goals allocated for processing were demonstrated by small volume quantities that were extrapolated by cost analyses to large-volume production. Program redirection precluded planned large-volume demonstrations and, in the final phase of the Project, efforts were directed toward researchoriented processing to produce high-efficiency cells. High-efficiency crystalline silicon solar cells are continuing to evolve in research laboratories. When efficiency increases resulting from these new cell designs level off, there is a need to develop high-volume, low-cost processes that will retain these efficiency improvements and capture the economic benefits.

To provide proper focus and coverage of the Process Development effort, four separate technology sections are discussed in this document: surface preparation, junction formation, metallization, and module assembly.

## Foreword

Throughout U.S. history, the Nation's main source of energy has changed from wood to coal to petroleum. It is inevitable that changes will continue as fossil fuels are depleted. Within a lifetime, it is expected that most U.S. energy will come from a variety of sources, including renewable energy sources, instead of from a single type of fuel. More than 30% of the energy consumed in the United States is used for the generation of electricity. The consumption of electricity is increasing at a faster rate than the use of other energy forms and this trend is expected to continue.

Photovoltaics, a promising way to generate electricity, is expected to provide significant amounts of power in years to come. It uses solar cells to generate electricity directly from sunlight, cleanly and reliably, without moving parts. Photovoltaic (PV) power systems are simple, flexible, modular, and adaptable to many different applications in an almost infinite number of sizes and in diverse environments. Although photovoltaics is a proven technology that is cost-effective for hundreds of small applications, it is not yet cost-effective for large-scale utility use in the United States. For widespread economical use, the cost of generating power with photovoltaics must continue to be decreased by reducing the initial PV system cost, by increasing efficiency (reduction of land requirements), and by increasing the operational lifetime of the PV systems.

In the early 1970s, the pressures of the increasing demand for electrical power, combined with the uncertainty of fuel sources and ever-increasing prices for petroleum, led the U.S. Government to initiate a terrestrial PV research and development (R&D) project. The objective was to reduce the cost of manufacturing solar cells and modules. This effort, assigned to the Jet Propulsion Laboratory, evolved from more than a decade-and-a-half of spacecraft PV power-system experience and from recommendations of a conference on Solar Photovoltaic Energy held in 1973 at Cherry Hill, New Jersey.

This Project, originally called the Low-Cost Solar Array Project, but later known as the Flat-Plate Solar Array (FSA) Project, was based upon crystalline-silicon technology as developed for the space program. During the 1960s and 1970s, it had been demonstrated that photovoltaics was a dependable electrical power source for spacecraft. In this time interval, solar-cell quality and performance improved while the costs decreased. However, in 1975 the costs were still much too high for widespread use on Earth. It was necessary to reduce the manufacturing costs of solar cells by a factor of approximately 100 if they were to be a practical, widely used terrestrial power source.

The FSA Project was initiated to meet specific cost, efficiency, production capacity, and lifetime goals by R&D in all phases of flat-plate module (non-concentrating) technology, from solar-cell silicon material purification through verification of module reliability and performance.

The FSA Project was phased out at the end of September 1986.

## Acknowledgments

Authorities in the field were used throughout this program as consultants to provide critiques, participate in critical technology reviews, and address specific technical problems. J. Parker, of Electrink Inc., and R. Vest, Director of the Turner Laboratory at Purdue University, were consultants in the area of material science; M. Wolf, of the University of Pennsylvania, consulted in the area of modeling and economics of specific processes; K. Wang, of the University of California, Los Angeles, consulted in the area of device physics; and Theodore Barry and Associates in production management.

Jet Propulsion Laboratory staff members were involved in laboratory research, technology critiques, process and problem analyses, and the technical management of contracts. The following engineers contributed to this program: D. Bickler (Area Manager), P. Alexander, D. Burger, J. Behm, D. Boyd, D. Fitzgerald, B. Gallagher, W. Hasbach, R. Josephs, A. Lawson, L. Sanchez, E. Drouet, C. Olson, and C. Radics. The contributions of support personnel, which included E. Fortier, L. Gee, K. Gray, L. Midling, J. Knox, and J. Stebbins, are gratefully acknowledged.

This document reports on work done under NASA Task RE-152, Amendment 419, DOE/NASA IAA No. DE-A101-85CE89008.

## FSA Project Summary

The Flat-Plate Solar Array (FSA) Project, a Government-sponsored photovoltaic (PV) project, was initiated in January 1975 with the intent to stimulate the development of PV systems for economically competitive, large-scale terrestrial use. The Project's goal was to develop, by 1985, the technology needed to produce PV modules with 10% energy conversion efficiency, a 20-year lifetime, and a selling price of \$0.50/W<sub>p</sub> (in 1975 dollars). The key achievement needed was cost reduction in the manufacture of solar cells and modules.

As manager, the Jet Propulsion Laboratory organized the Project to meet the stated goals through research and development (R&D) in all phases of flat-plate module technology, ranging from silicon-material refinement through verification of module reliability and performance. The Project sponsored parallel technology efforts with periodic progress reviews. Module manufacturing cost analyses were developed that permitted cost-goal allocations to be made for each technology. Economic analyses, performed periodically, permitted assessment of each technical option's potential for meeting the Project goal and of the Project's progress toward the National goal. Only the most promising options were continued. Most funds were used to sponsor R&D in private organizations and universities, and led to an effective Federal Government-University-Industry Team that cooperated to achieve rapid advancement in PV technology.

Excellent technical progress led to a growing participation by the private sector. By 1981, effective energy conservation, a leveling of energy prices, and decreased Government emphasis had altered the economic perspective for photovoltaics. The U.S. Department of Energy's (DOE's) National Photovoltaics Program was redirected to longerrange research efforts that the private sector avoided because of higher risk and longer payoff time. Thus, FSA concentrated its efforts on overcoming specific critical technological barriers to high efficiency, long life, reliability, and low-cost manufacturing.

To be competitive for use in utility central-station generation plants in the 1990s, it is estimated that the price of PV-generated power will need to be \$0.17/kWh (1985 dollars). This price is the basis for a DOE Five-Year Photo-voltaics Research Plan involving both increased cell efficiency and module lifetime. Area-related costs for PV utility plants are significant enough that flat-plate module efficiencies must be raised to between 13 and 17%, and module life extended to 30 years. Crystalline silicon, research solar cells (non-concentrating) have been fabricated with more than 20% efficiency. A full-size experimental 15% efficient module also has been fabricated. It is calculated that a multimegawatt PV power plant using large-volume production modules that incorporate the latest crystalline silicon technology could produce power for about \$0.27/kWh (1985 dollars). It is believed that \$0.17/kWh (1985 dollars) is achievable, but only with a renewed and dedicated effort.

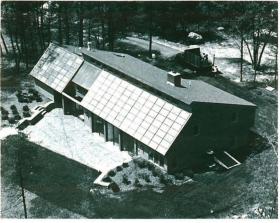

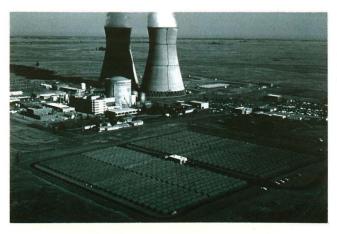

Government-sponsored efforts, plus private investments, have resulted in a small, but growing terrestrial PV industry with economically competitive products for stand-alone PV power systems. A few megawatt-sized, utilityconnected, PV installations, made possible by Government sponsorship and tax incentives, have demonstrated the technical feasibility and excellent reliability of large, multimegawatt PV power-generation plants using crystalline silicon solar cells.

## Major FSA Project Accomplishments

- Established basic technologies for all aspects of the manufacture of nonconcentrating, crystalline-silicon PV modules and arrays for terrestrial use. Module durability also has been evaluated. These resulted in:

- Reducing PV module prices by a factor of 15 from \$75/W<sub>D</sub> (1985 dollars) to \$5/W<sub>D</sub> (1985 dollars).

- Increasing module efficiencies from 5 to 6% in 1975 to more than 15% in 1985.

- Stimulating industry to establish 10-year warranties on production modules. There were no warranties in 1975.

- Establishing a new, low-cost high-purity silicon feedstock-material refinement process.

- Establishing knowledge and capabilities for PV module/array engineering/design and evaluation.

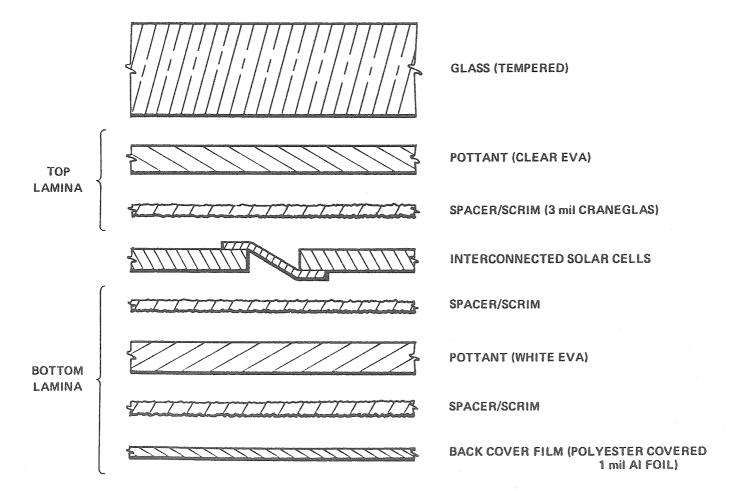

- Establishing long-life PV module encapsulation systems.

- Devising manufacturing and life-cycle cost economic analyses.

- Transferred technologies to the private sector by interactive activities in research, development, and field demonstrations. These included 256 R&D contracts, comprehensive module development and evaluation efforts, 26 Project Integration Meetings, 10 research forums, presentations at hundreds of technical meetings, and advisory efforts to industry on specific technical problems.

- Stimulated the establishment of a viable commercial PV industry in the United States.

## Process Development Summary

The Process Development Area of the Flat-Plate Solar Array Project was initiated with the following goals: develop low-cost solar cell and module processes, design facilities and equipment to perform the processes, demonstrate fabrication in a pilot line, and transfer technology to industry. The terrestrial photovoltaics program was changed in 1981 to emphasize high-efficiency cell research. Facility and equipment design were curtailed and pilot line contracts redirected toward research. Research efforts were increased on the effects of processing on cell performance and in development of new processes in support of high-efficiency cell designs.

Accomplishments of 11 years of activity, in which more than 75 contracts were let, are grouped into two categories: low-cost processes and high-efficiency cell process research. These accomplishments are briefly mentioned below in each of four major technology areas: surface preparation, junction formation, metallization, and assembly:

- Surface preparation accomplishments related to low-cost cell fabrication were:

- Development of alkaline etches for damage removal and texturizing.

- Automation studies for reduced labor input.

- Meniscus coating technology for pinhole-free films.

- Screen-printed coatings for metal patterning.

High-efficiency cell surface preparation process research showed:

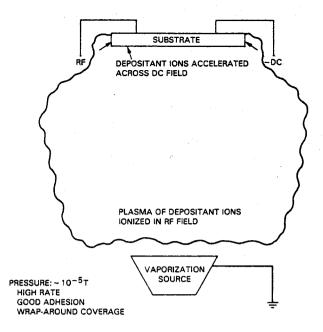

- Plasma processes are clean, but too slow.

- Two-layer antireflective coatings are feasible and desirable.

- Maintenance of surface cleanliness during processing is important for high efficiency.

- Junction formation accomplishments for low costs were:

- Simultaneous front and back junction formation using liquid dopants.

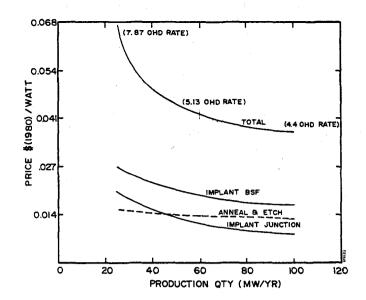

- High-rate ion implantation.

- Non-mass-analyzed ion implantation.

High-efficiency cell efforts resulted in:

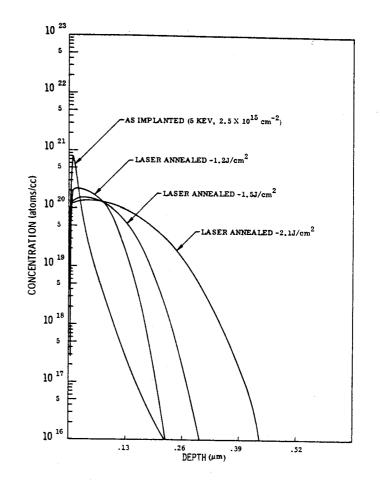

- Laser annealing using both solid-state and excimer laser technology.

- Pulsed electron beam annealing.

- Rapid thermal pulse annealing.

- Metallization processing was a special interest area because of its cost and reliability impact. Low-cost

processing accomplishments were:

- Thick-film, screenable ink printing with silver, aluminum, aluminum-silver, and copper.

- Metallo-organic decomposition (MOD).

- Silver-bismuth ink and liquid applications.

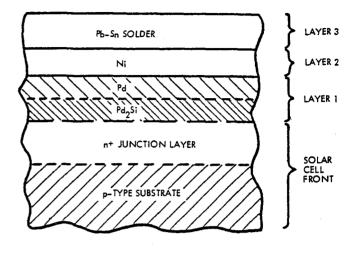

- Reliable plating systems using palladium, nickel, and copper.

- Initial high-efficiency cell processes in the area of laser pyrolytic decomposition of MOD films and producing reliable diffusion barrier films.

- Module assembly processes aimed at low-cost fabrication are directly transferrable to high-efficiency modules. Key accomplishments were:

- Fully automated interconnection by soldering or by ultrasonic bonding.

- Demonstration of robotic module assembly.

- In-line ultrasonic cleaning.

- Demonstration of automated module lay-up equipment.

- Development of lamination process and equipment.

- Demonstration of robotic terminal assembly and inspection.

The need to reduce costs was met by development and demonstration of processes that met Project goals for costs. Many new processes and equipment were developed; some are now standards in the industry. Pilot line operation was not accomplished because of redirection. Transfer of technology to industry was achieved with more than 140 processes documented. In the future, when new higher-efficiency solar cell designs are developed, it is anticipated that some new processes and equipment will be required for low-cost production that retains the efficiency improvements.

## Contents

| I.   | INT    | RODUCTION                                    | 1 |

|------|--------|----------------------------------------------|---|

|      | Α.     | OBJECTIVES                                   | 1 |

|      | В.     | GOALS                                        | 1 |

|      | C.     |                                              | 1 |

|      |        | 1. Phase I: Technology Assessment            | 1 |

|      |        | 2. Phase II: Process Development             | 2 |

|      |        | 3. Phase III: Facility and Equipment Design  | 3 |

|      |        | 4. Phase IV: Experimental Plant Construction | 3 |

|      | D.     | PROJECT REDIRECTION                          | 3 |

|      | E.     | SUMMARY COMMENTS                             | 4 |

| II.  | SUF    | RFACE PREPARATION                            | 5 |

|      | A.     |                                              | 5 |

|      | В.     |                                              | 5 |

|      |        | 1. Texturizing                               |   |

|      |        | 2. Antireflective Coating                    |   |

|      | C.     | STATUS AS OF 1975                            |   |

|      |        | 1. Damage Removal and Texturizing            |   |

|      |        | 2. Cleaning                                  | 3 |

|      |        | 3. Rinsing and Drying                        | 3 |

|      |        | 4. Metal Patterning                          | 3 |

|      |        | 5. Antireflective Coating 6                  | 3 |

|      | D.     | PROCESS DEVELOPMENT                          | , |

|      |        | 1. Phase I                                   | , |

|      |        | 2. Phase II                                  | , |

|      | E.     | RELIABILITY                                  | ) |

|      | F.     | ECONOMICS                                    | ) |

|      | G.     | KEY ACCOMPLISHMENTS                          | ) |

|      | Н.     | CURRENT STATUS                               |   |

|      | ١.     | REQUIRED FUTURE TECHNICAL NEEDS              |   |

| III. | II INI | CTION FORMATION                              |   |

|      | A.     | BACKGROUND                                   |   |

|      | A.     |                                              |   |

|                                        | В.       | THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13 |

|----------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                        | Ξ.       | 1. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                                        |          | 2. Forming Junctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                                        | C.       | PROCESS DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

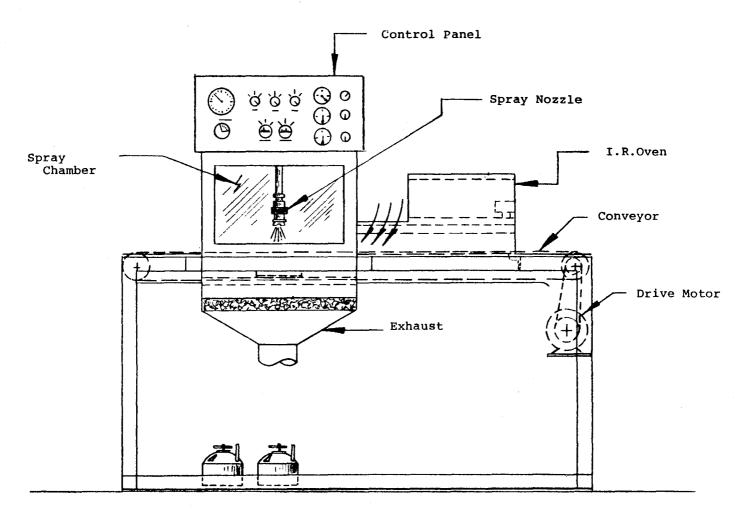

|                                        |          | 1. Junction Formation by Spray-on of Liquid Dopants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|                                        |          | 2. Junction Formation by Spin-on of Liquid Dopants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 |

|                                        |          | 3. Aluminum-Printed Back Junction Formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |

|                                        |          | 4. Gaseous Diffusion Junction Formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17 |

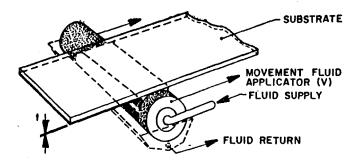

|                                        |          | 5. Liquid Dopant Coating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

|                                        |          | 6. Ion Implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

|                                        |          | 7. Non-Mass-Analyzed Ion Implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

|                                        |          | 8. Ion Implantation of Silicon Sheet Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

|                                        |          | 9. Pulsed Electron Beam Annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18 |

|                                        |          | 10. Excimer Laser Annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18 |

|                                        |          | 11. Nd: Glass Laser Annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

|                                        |          | 12. Module Experimental Process System Development Unit Junction Formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19 |

|                                        |          | 13. Rapid Thermal Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19 |

|                                        | D.       | RELIABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19 |

|                                        | E.       | ECONOMICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

|                                        | F.       | KEY ACCOMPLISHMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20 |

|                                        | G.       | CURRENT STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

|                                        | Н.       | REQUIRED FUTURE TECHNOLOGY NEEDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21 |

| IV.                                    | МЕТ      | TALLIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00 |

| IV.                                    | A.       | BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                                        | А.<br>В. | THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

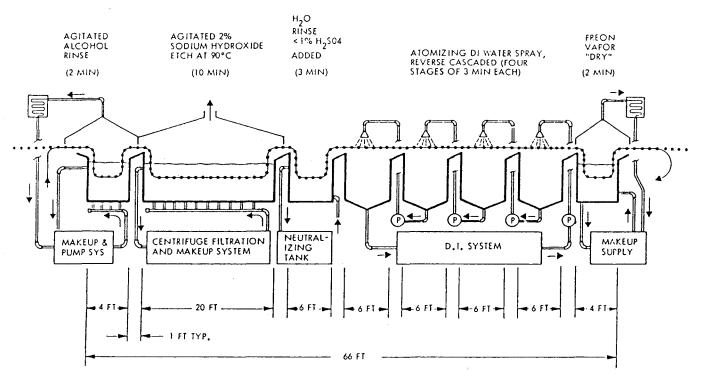

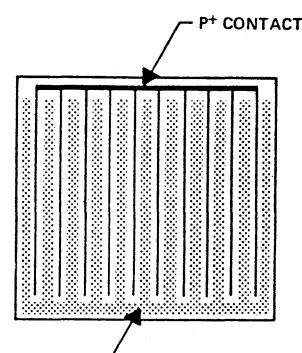

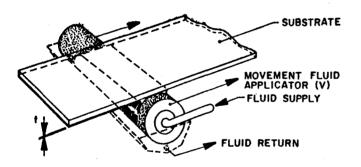

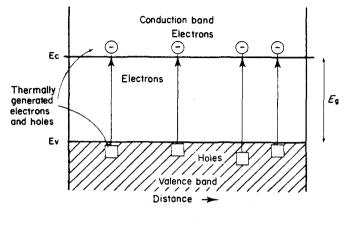

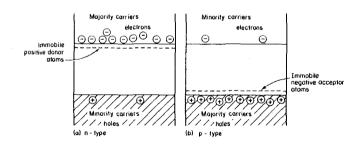

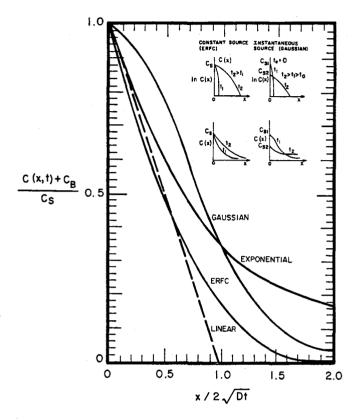

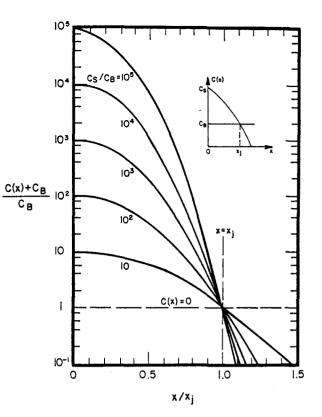

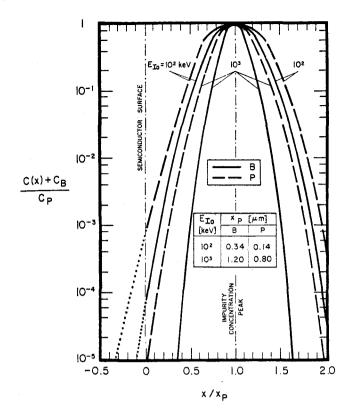

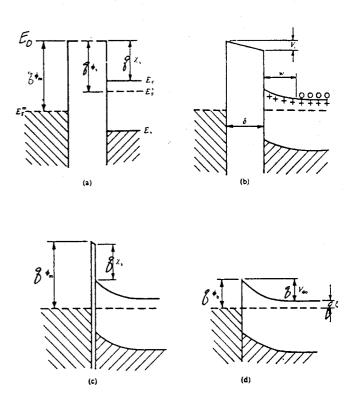

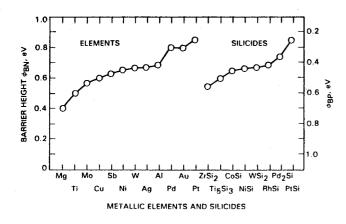

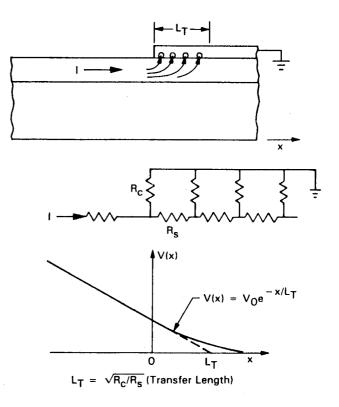

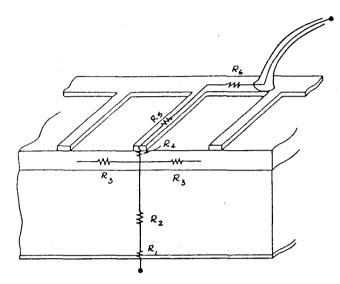

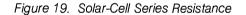

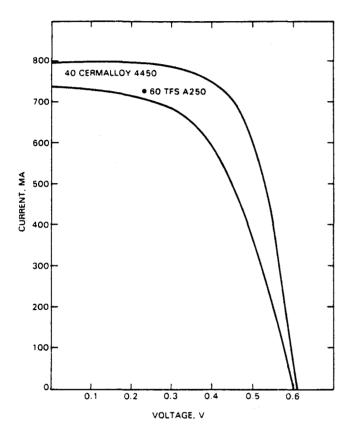

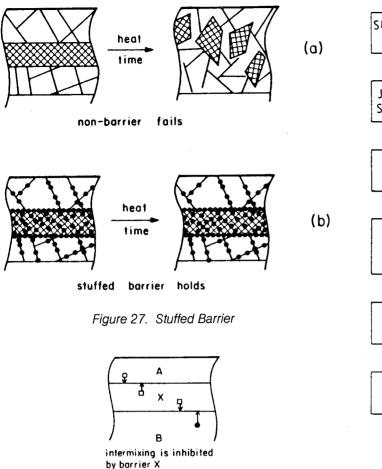

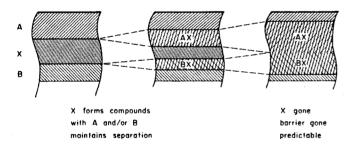

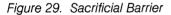

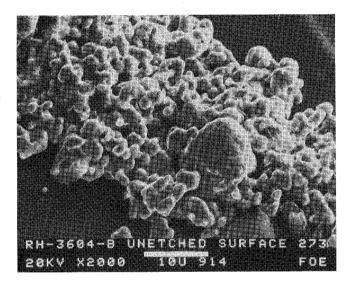

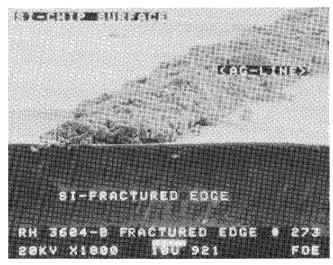

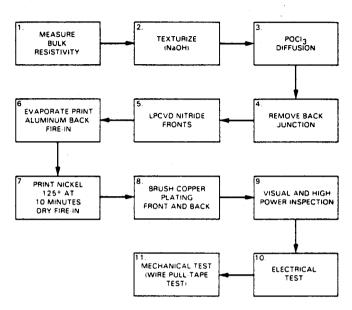

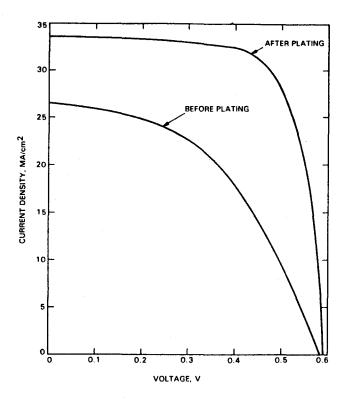

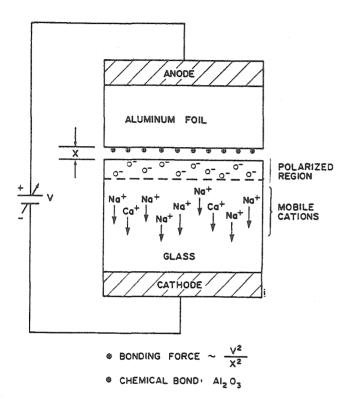

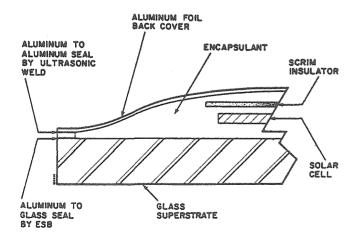

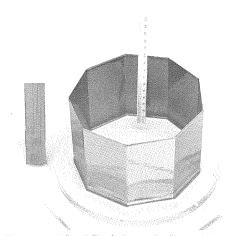

|                                        | <b>.</b> | 1. Metal Semiconductor Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |